در میان ریزمعماریهای اینتل، طراحی Skylake را میتوان به عنوان طولانیترین الگوی موجود در چرخه تولید و بهینهسازی در نظر گرفت. کمپانی نامبرده از این موضوع به نفع خود بهره برده و با ایجاد بهبودهای چشمگیر در بخش سلسله مراتب پردازندههای چند هستهای و سری HEDT خود بستری را جهت افزایش ظرفیت حافظه پرسرعت کش سطح دوم و کاهش وابستگی بالای تراشهها به کش اشتراکی سطح سوم را به ارمغان آورده است. کمپانی اینتل تعادل سنتی حافظه کش خود را در بخش پردازشگرهای رده موبایل و دسکتاپ حفظ کرده و تنها به پیادهسازی بهبود اشاره شده در پردازندههای سری HEDT خود پرداخته است. بر طبق جدیدترین فهرست بندی دیتابیس آنلاین Geekbench برای یک واحد سیپییو چهار هستهای “Tiger Lake-Y”، این موضوع میتواند تغییراتی بعضاً بنیادینی را در زیرمعماری Tiger Lake، بهخصوص هستههای فیزیکی مورد استفاده در الگوی “Willow Cove” فراهم آورد.

با فرض درست بودن ورودی ثبت شده در پایگاه داده Geekbench و عدم وجود اشتباهات تایپی در فهرست بندی انجام شده، پردازنده Tiger Lake-Y اشاره شده در پاراگراف پیشین از تعداد چهار هسته فیزیکی و هشت رشته پردازشی بهره برده و میزان گنجایش حافظه کش سطح دوم آن برابر با مقدار چشمگیر 1280 کیلوبایت بر هر هسته (مجموع 1.25 مگابایت) در نظر گرفته است. این میزان در مورد حافظه کش سطح سوم مساوی با 12 مگابایت بهصورت مشترک در بین تمامی هستههای موجود میباشد. کمپانی اینتل علاوه بر آن میزان گنجایش حافظه L1D (کش سطح یک داده) را نیز به 48 کیلوبایت افزایش داده است، اما ظرفیت کش L1I (کش سطح یک دستورالعملها) تغییری را به خود ندیده و برابر با 32 کیلوبایت در نظر گرفته شده است.

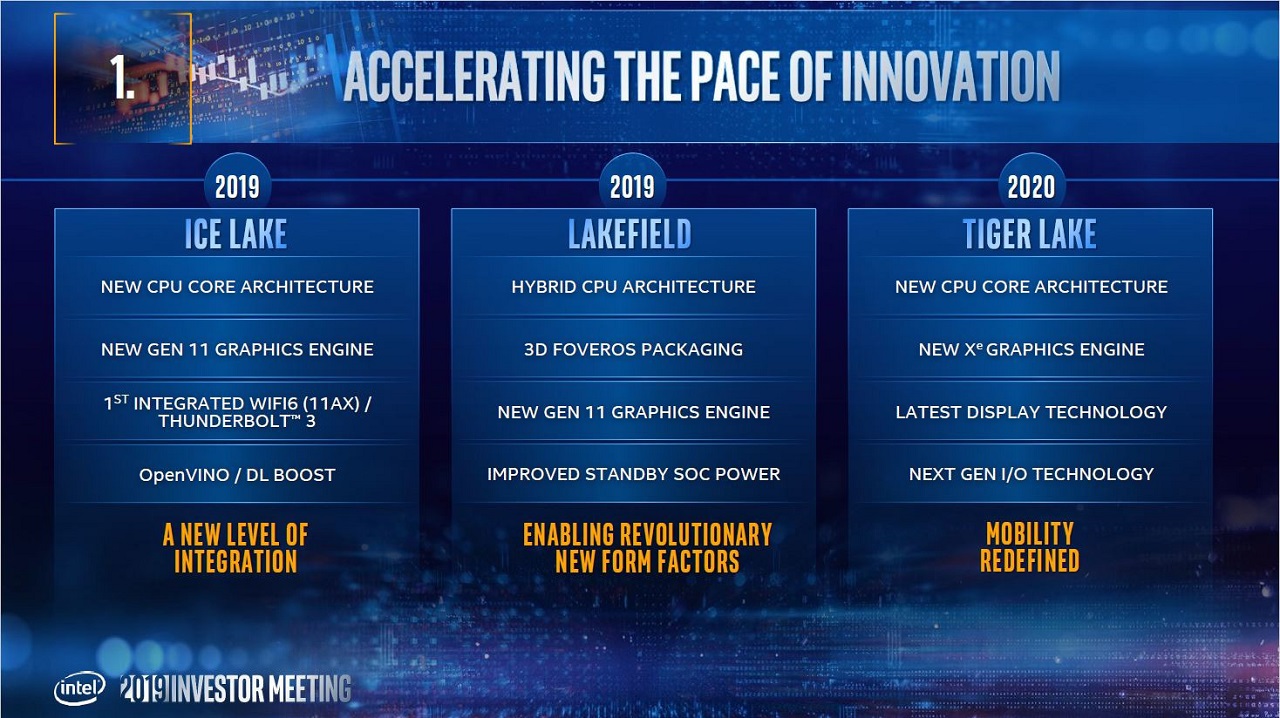

مقادیر اشاره شده نمایانگر افزایش 400 درصدی در بخش حافظه کش L2 و 50 درصدی در بخش حافظه کش L3 میباشند که در نوع خود بیسابقه است! برخلاف ریزمعماری “Skylake-X”، افزایش گنجایش حافظه کش سطح دوم به کاهش ظرفیت کش سطح سوم منتهی نشده است. سیپییو Tiger Lake-Y مورد بحث توسط یک پلتفرم آزمایشی “Corktown” مورد تست و بررسی قرار گرفته است. انتظار میرود تا ریزمعماری “Tiger Lake” به عنوان جایگزینی بر الگوی “Ice Lake” در سال 2020 تا 2021 میلادی معرفی شده و در دسترس قرار گیرد.

منبع: TechPowerUP